## A Review of Prognostics and Health Management for Power Semiconductor Modules

Nicolas Degrenne<sup>1</sup>, Jeffrey Ewanchuk, Erwan David, Roman Boldyrjew and Stefan Mollov

Mitsubishi Electric R&D Centre Europe, Rennes, 35708, France <sup>1</sup>n.degrenne@fr.merce.mee.com

## ABSTRACT

In this paper, a review of current techniques used in the prognostics and state-of-health monitoring for power semiconductor modules is provided. Given the increasing trend in power modules having a larger share of the power electronic market, understanding their lifetime limitations is critical to improving the life-cycle cost of the power electronic product. Hence, this paper reviews common failure mechanisms in power modules and the state-of-art in predicting the lifetime of the module based on a given mission profile. Prognostics are reviewed in terms of stressbased and condition monitoring-based methods, while the potential of prognostics is presented for applications that utilize power modules.

#### **1. INTRODUCTION**

Owing to their lowered parasitic construction, high performance and relatively low manufacturing effort, power semiconductor modules are often preferred in applications where the power exceeds a few kilo-watts. This preference in higher power applications can be further appreciated by the fact that lower cost dies can be easily paralleled within a single power module to increase the rating of that module without having to manufacture a single large power die (Wintrich, Nicolai, Tursky & Reimann, 2011). Hence, since 2008, the market size for power modules occupies a larger proportion of the total market for power electronic devices with a predicted market share of 30% by 2020 (Madjour, 2014).

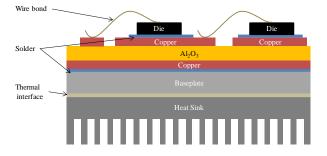

Power modules are constructed with several mechanical layers, as seen in Figure 1. Commonly, the die is attached to a DBC (direct bonded copper), via solder, that is composed of a bonded copper-ceramic-copper structure, allowing electrical isolation but with high thermal conductivity towards the heatsink. In order to mate the DBC with the heatsink and increase the thermal capacity of the system, a

base-plate is also typically used in medium and high power modules (Wintrich et al. 2011).

Furthermore, using a thermally conductive interface material, the module (base-plate-DBC-die) is attached to the heatsink, completing the thermal extraction path. In this paper, the presence of these layers within the power module is a critical aspect for determining its lifetime.

Depending on the application of a power converter, the power devices and the capacitors can exceed half the reported failures - with power devices being the largest single component (Yang, Bryant, Mawby, Xiang, Ran & Tavner, 2011). These failures are typically a result of environmental factors, overload conditions, and system transients (Yang et al. 2011). Hence, in difficult-to-service applications such as off-shore wind converters, there is an increasing amount of pressure to predict maintenance intervals and improve replacement costs by studying the reliability of power modules, (Ma, Liserre, Blaabjerg, & Kerekes, 2014). These same techniques have also found their way into automotive applications, where the application conditions vary widely and the reliability of the converter is less deterministic (Hirschmann, Tissen, Schröder & De Doncker, 2007). In both applications, the total lifecycle cost of the converter can be decreased with proper prediction of the lifetime. Hence, this paper provides a review of prognostic and health management techniques

Nicolas Degrenne et al. This is an open-access article distributed under the terms of the Creative Commons Attribution 3.0 United States License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

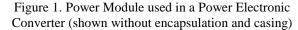

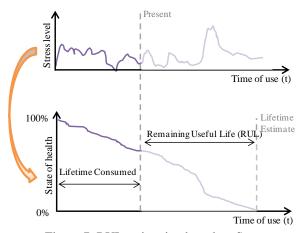

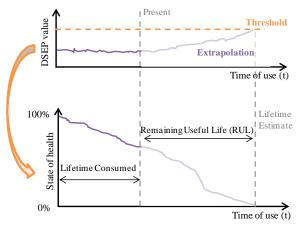

for power modules, with the aim of predicting the remaining useful life of the power module, as illustrated in figure 2.

As the chief aim of the paper is to review the methods relevant to lifetime prediction of power modules, section 2 of this paper covers the failure mechanisms present in typical IGBT-based power modules. In section 3, mission profile based lifetime estimation techniques are presented, with stress-based and condition monitoring-based prognostic methods highlighted in sections 4 and 5 respectively. Finally, section 6 details some potential applications for prognostics in power modules.

Figure 2. Remaining useful lifetime of a power module

## 2. FAILURE MECHANISMS

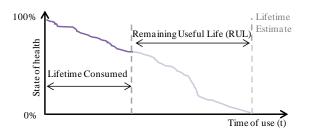

The aging of devices is caused by different material properties of adjacent layers, as shown in Figure 1, specifically due to the different coefficients of thermal expansion (CTE) leading to a bimetal-like effect. Hence, during heat-up and cool-down phases the dissimilar expansion of adjacent layers causes a shear stress along the contact surface. Two principal failure mechanisms have been identified to be responsible for wear: bond wire lift-off and solder fatigue (Lutz, Schlangenotto, Scheuermann & De Donker, 2011) (Fig. 3). Reconstruction of metallization is mentioned in the literature as a third failure mechanism but it is not completely investigated yet (Lutz et al. 2011), (Wu, Held, Jacob, Scacco & Birolini, 1995), (Wintrich et al. 2011).

## 2.1. Bond wire lift-off

Bond wire is a cost-effective process to make an interconnection with the source, on the top of the die. Usually, bond wires are made of Al and have therefore a higher CTE value than Si dies. Hence bond wires expand more than the connected chip. As a consequence wires themselves are under stress caused by bending and the interface between bond and chip is under shear stress (Wintrich et al. 2011).

Degradation starts usually at the edges of the interface and is presented as crack growth. The cracks generally spread around grain boundaries above the interface, in the wire bond. A reasonable explanation for this is that a softening and hardening occurs during the bonding process, leading to

## Figure 3. Bond wire (left) and solder (right) cracks. Pictures from ECPE workshop on "reliability and lifetime estimation". 2013.

a higher reliability of the interconnection and a reduced reliability of the bond wire itself (Onuki, Koizumi & Suwa, 2000). Cracks grow towards the center of the interconnection, decreasing the contact area. Therefore the electrical resistance is increasing, measurable as a growing of forward voltage drop. Consequently, the power losses rise up leading to a higher junction temperature during power-on time. Eventually higher thermo-mechanical stress will finally lead to a bond wire lift-off. A single lift-off will accelerate the degradation process, because the full load current will increase the current per bond for the remaining wires leading to higher temperature at the interconnection (Goehre, Schneider-Ramelow, Geißler & Lang, 2010), (Lutz et al. 2011). (Onuki et al. 2000). (Baverer, Herrmann, Licht, Lutz & Feller, 2008). The last bond wire carrying the highest current density typically leaves a crater just under its heel after lifting-off. Such a crater is usually a characteristic of an arc flash-over (Lutz et al. 2011). The lifetime of bond wires has increased lately thanks to better bond alloys, improved bonding technology and optimization of the bond wire geometry (Amro, Lutz, Rudzki, Sittin & Thoben, 2006).

#### 2.2. Solder delamination

Solder fatigue is the second most common aging mechanism in power modules. In popular semiconductor power modules there are two solder layers where solder fatigue occurs: within the solder between base-plate and DBC or chip and DBC. Stresses cause fractures formation inside the solder interfaces. With Pb-based solders, delamination starts usually in the edges and corners of the layer and is spreading towards centre. The thermal impedance is increased, thereby raising the junction temperature of the die. In this manner, higher thermo-mechanical stress accelerates the aging in a positive feedback loop (Lutz et al. 2011). During the last couple of years, Pb-free solder layers were investigated (Morozumi, Yamada, Miyasaka, Sumi & Seki, 2003), (Herrmann, Feller, Lutz, Bayerer & Licht, 2007). It was shown that with Sn/Ag solder, cracks originate in the center and spread in vertical and reticulated structures at tin grain boundary. It was also shown that Pb-free solder layers lead to higher reliability even if bond wires haven't been improved (Hensler, Lutz, Thoben & Guth, 2010). indicating a cross-coupling reliability effect between the top- and bottom-side die terminations.

The aging of solder joints can be detected by scanning acoustic microscopy (SAM) and by calculating thermal resistance during the test. Usually, the end-of-life criterion from semiconductor power modules is reached when the thermal resistance has increased by more the 20% (Hensler et al. 2010).

### 3. MISSION PROFILE BASED LIFETIME ESTIMATION

Design for reliability consists in designing a power module not only with respect to functional requirements but also to reliability requirements (Lu, Bailey & Yin, 2009). It requires estimating lifetime of the module under study, usually with minimum reliability figure in mind

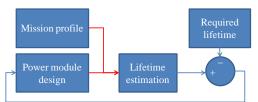

The lifetime estimation is generally obtained with a stepwise approach (Mainka, Thoben & Schilling 2011) from an estimation of the usage (mission profile). It employs an electrical, thermal and damage model of the Device Under Test (DUT) (Fig. 4). This approach assumes that the device will be used according to the pre-defined mission profile, and that the device assembly will endure a known number of stress cycles (Fig. 5), an assumption that is difficult to fulfill in reality.

Figure 4. Design for reliability

Figure 5. Mission profile-based methods can be used in applications where usage is well identified

## **3.1.** From mission profile to junction temperature profile

A number of application-specific mission profiles have been defined. Solar radiation profiles are used in photovoltaic applications (Yang, Wang & Blaabjerg 2015), wind profiles in wind power applications (Ma et al. 2014), sea elevation profiles for direct wave energy converter (Kovaltchouk, Aubry, Multon & Ben Ahmed, 2013) or drive cycle for automotive domain as detailed below.

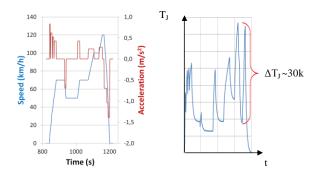

A mission profile in automotive application can be derived from a speed profile representative of the average driving style. A collection of driving styles corresponding to different types of driving categories is available in the literature (Barlow, Latham, Mccrae & Boulter 2009) such as FTP-72 (Hirschmann, Member, Tissen, Schröder & Doncker, 2007) or NEDC (Biela, Waffler, & Kolar, 2009) as shown in Fig. 6.

The loss profile of each die in the power module is translated from the mission profile by considering traction chain characteristics and various parameters related to the motor and the converter (Thoben, 2008). A thermal model is then applied and results in a junction temperature profile  $T_J$  (Lu et al., 2009)(Fig. 6). Note that  $T_J$  is fed back in the calculation of the power losses.

Figure 6. NEDC driving cycle (left) (blue: speed, red:

# **3.2. From junction temperature profile to lifetime estimation**

A counting method is used to extract and classify the thermal cycles. The rainflow algorithm is able to capture compound temperature variations, and is considered to be amongst the better performing algorithms (Mainka et al. 2011).

The stresses are converted into damage with a damage model. This model is either derived from physical models (Kovacevic, Drofenik & Kolar, 2010) or with data-driven approach using power cycling tests (Scheuermann & Schmidt, 1997). Different models are commonly used such as Coffin-Manson (Halford & Manson, 1967), LESIT (Held, Jacob, Nicoletti, Scacco & Poech, 1997), CIPS08 (Bayerer, Hermann, Licht, Lutz & Feller, 2008),

The damages are then summed using Palmgren-Miner linear accumulation rule (Miner, 1945), though this is increasingly questioned (Aal, 2014). In (Huang & Mawby, 2013), the damage level is fed-back to the thermal model. The lifetime is calculated based on the duration of the mission profile and the corresponding computed damage. Based on the lifetime estimation, the design can be adjusted to meet the reliability requirements.

#### 4. STRESS-BASED PROGNOSTICS

Analyzing a pre-defined mission profile provides insight into potential reliability problems that may or may not develop during the life of a product. Although such insight is beneficial during the design and the operational phases of the product, the information quickly becomes obsolete once the product usage (e.g. operating and environmental characteristics) deviates significantly from the assumed operating conditions that have been originally analysed. That is why monitoring of real-life operating and environmental conditions is used to derive the reliability problems based on the actual operating and environmental conditions.

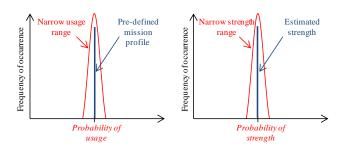

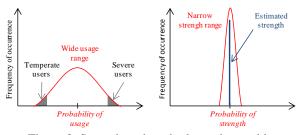

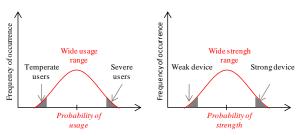

Stress-based methods quantify the cause of degradation: stress (Fig. 7). They are most adequate when the manufacturing process deviations (i.e. strength range) are narrow and when the usage cannot be easily pre-defined or has large deviations (Fig. 8).

Figure 7. RUL estimation based on Stress

In order to estimate the stress, the methods relying on power and thermal models (as presented in section 3) can be implemented in real-time. Alternatively, the junction temperature  $T_J$  can be measured on-line. Then, the stress is quantified with a real-time algorithm and converted to a State-of-Health (SoH). The SoH is extrapolated to estimate the End-of-Life (EoL) and the Remaining Useful Life (RUL).

#### 4.1. Junction temperature measurement

A first approach is to position a conventional thermal sensor in the vicinity of the power chip. Commercially available negative temperature coefficient (NTC) thermistors operate up to 200°C, and can be attached with standard processes (e.g. sintering, wire-bonding). This approach measures the temperature several millimeters away from the junction, and has a low space and time resolution, the relevance of the provided information is thus questionable.

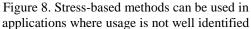

A second approach is to create a temperature sensor on the silicon power die itself. In a patent, Schuler (2011) develops the idea of a thermocouple circuit formed by two bonding wires and a pad to measure the temperature difference between the chip and the carrier. In (Motto & Donlon 2012), a string of diodes is fabricated on the IGBT chip's surface (Fig. 9). The linear dependence of the forward voltage drop is used to estimate temperature. This solution has the required performance but is not cost-effective as it occupies a valuable real estate on the power die.

Figure 9. IGBT chip current and temperature sensors (Motto et al. 2012)

A third approach is to monitor Thermo-Sensitive Electrical Parameters (TSEP), inherent to the semiconductor device (Avenas, Dupont & Khatir, 2012), (Baker, Liserre, Dupont & Avenas, 2014). Some TSEPs such as voltage drop at low current and saturation current have to be done in specific electrical conditions and often necessitate an alteration to the structure or operation of a power electronic converter. Table 1 compares methods that can be performed online, either during the conduction time or the switching time. All these methods require accurate sensors and chip-level calibration. They must be compared in terms of linearity, dependence in operating conditions outside of temperature, sensitivity and implementation cost. Converter-level methods such as low-order harmonics identification in an inverter (Xiang, Ran, Tavner, Yang, Bryant & Mawby, 2012) are not included in the table.

| TSEP                                                                                                                                                                                                          | Reference                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage at high current<br>of transistors and diodes                                                                                                                                                          | (Kim & Sul, 1998)<br>(Perpiñà, Serviere & Saiz, 2006)<br>(Koenig & Plum, 2007)<br>(Lutz, Paul & Zill, 2011)<br>(Dupont, Avenas & Jeannin 2013)    | Requires very accurate sensors and high-voltage protection. Sensitivity of approx. 20mV/°C. Measurement influenced greatly by parasitic elements inside power modules (bond wires, etc.), and load current. Is also a DSEP (Table 2).                                                                                    |

| Turn-off transition time<br>of IGBT transistors                                                                                                                                                               | (Barlini & Ciappa, 2006)<br>(Kuhn & Mertens, 2009)<br>(Bryant, Yang, Mawby, Xiang, Ran, Tavner &<br>Palmer, 2011)<br>(Xu, Jiang, Li & Ning, 2013) | Sensitivity of approx. 2ns/K. Changes have also been viewed in harmonics in the output of an IGBT inverter.                                                                                                                                                                                                              |

| Turn-on delay and/or<br>di/dt of transistors                                                                                                                                                                  | (Barlini & Ciappa, 2007)<br>(Kuhn & Mertens, 2009)<br>(Sundaramoorthy, Bianda, Bloch & Zurfluh,<br>2014)                                          | Increase in gate resistance during the measurement is proposed to slow down the process. Sensitivity of approx. 2ns/K or 40A/(µs.K) for high power IGBTs.                                                                                                                                                                |

| Threshold voltage of<br>MOS transistors                                                                                                                                                                       | (Chen, Pickert, Atkinson & Pritchard, 2006)<br>(Bahun, Sunde & Jakopovic, 2013)                                                                   | The sensing circuit can be implemented in the gate driver. The threshold voltage is measured when the current starts flowing through the transistor. Sensitivity of approx. 10mV/K.                                                                                                                                      |

| Gate parasitic (internal<br>resistance(Sundaramoorthy, Bianda, Bloch, Nistor,<br>Knapp & Heinemann, 2013)<br>(Baker, Munk-Nielsen, Liserre & Iannuzzo,<br>2014)<br>(Niu & Lorenz, 2014)<br>(Niu&Lorenz, 2015) |                                                                                                                                                   | The sensing circuit can be implemented in the gate driver. The sensed parameter can either be the duration of the Miller plateau phase (approx. 1.2ns/K), the voltage during turn-on delay (approx. 20mV/K), the gate charge (approx. 250pC/K) or the gate current transient such as the peak current (approx. 2.5mA/K). |

#### 4.2. Real-time stress-counting algorithms

The rainflow algorithm traditionally uses the entire time history of the junction temperature. This approach is inconvenient in real-time applications because the algorithm must be applied periodically to large datasets. A first option is to use the rainflow algorithm on windows of data of e.g. 1 day in order to reduce the size of the dataset. A second option is to use another type of stress-counting algorithm. Three alternative real-time stress-counting algorithms are evaluated with respect to wire-bond and chip solder failures in (Mainka et al. 2011). The rising edge and half-cycle methods process each minima and maxima value as it occurs and give acceptable results. An on-line stress-couting algorithm is used in (Musallam, Johnson, Yin, Bailey & Mermet-Guyennet, 2010) and (James 2012), but the performances of the algorithms are not evaluated experimentally.

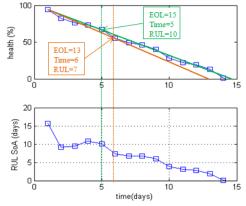

#### 4.3. State-of-Health extrapolation

The time history of the state of health is required to determine the RUL of a device. It is linearly extrapolated according to the following equation (Fig. 10):

$$RUL_n = \frac{n \times SoH_n}{100 - SoH_n}$$

with *n* the time variable, *SoH* the state of health (in %).

Figure 10. State-of-Health linear extrapolation to estimate EoL and RUL.

#### 5. CONDITION-MONITORING PROGNOSTICS

Unlike stress-based methods, condition-monitoring (CM) methods examine the consequence of degradation, i.e. the evolution in time of one or several Damage-Sensitive Electrical Parameters (DSEP), also mentioned as failure precursors (Fig. 11). As such, CM methods are useful in applications where devices present variations due to manufacturing process dispersion (Fig. 12).

Figure 11. RUL estimation based on Damage-Sensitive Electro Parameter (DSEP)

Figure 12. Condition monitoring can be used in applications where usage and/or strength is not well identified.

The selection of a DSEP depends on the preferred failure mode and on the ease of implementation. In order to convert the deviation of the DSEP into a RUL estimate, a threshold value is determined, and the time deviation is extrapolated (Fig. 11). Two approaches are opposed in the literature: (a) past-history approaches that only use past DSEP data on the DUT itself, and (b) model-based approaches that use data from other devices to generate a model.

#### 5.1. Damage Sensitive Electrical Parameters

Table 2 sums up the DSEP parameters that have been treated and reviewed (Yang, Xiang, Bryant, Mawby, Ran & Tavner, 2010) in the literature. In the case of solder degradation, all methods discussed in paragraph 3.1 to estimate the junction temperature are useful to estimate the value of  $R_{TH}$ . In the case of wire-bond failure (lift-off), the electrical path is suddenly degraded, and the voltage at high current experiences an abrupt, distinguishable increase.  $T_J$  increases as well, as a consequence to the loss increase. In order to isolate the impact of bond-wire degradation from solder-crack degradation, the impact of temperature on the

voltage can be compensated (Rashed, Forest, Huselstein, Martire & Enrici, 2013), (Ji, Pickert, Cao & Zahawi, 2013).

Note that on-line measurement may not be a requirement anymore for CM since it is possible to monitor health discontinuously, before or after the operation of the converter. In his thesis, Ji (2011) performs wire-bond and solder condition monitoring of an automotive inverter employing a calibrated operating point sequence taking approx. 5s. However, applications permitting such calibration procedures are rare in practice.

#### 5.2. DUT past-history approach

The prognostic algorithm only uses the past history of the device to estimate its health and the RUL. The extrapolation typically uses a regression framework based on either statistical or Markov chains.

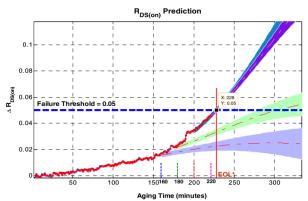

In (Celaya, Saxena, Saha, Vashchenko & Goebel, 2011), a Gaussian Process Regression (GPR) is used on discrete power MOSFETs. A distribution is tuned to fit available measurements, used to output a mean and covariance function, and to predict mean value and corresponding variance for a future point of interest (Fig. 13).

Past-history approach offers the advantage of requiring no training data set from other devices, even if domain knowledge is necessary to define the prior distribution and the type of covariance function. In (Celaya, Saxena, Saha & Goebel, 2011), the GPR method is compared to two model-based approaches discussed in the following section, and shown to be less efficient with respect to several prognostic performance metrics.

Figure 13. Prediction of RUL for aged device using GPR technique (Celaya, Saxena, Saha, Vashchenko & Goebel, 2011).

| DSEP                           | Reference                                                                                                                                                                                                                                                                                                                                    | Failure mechanism                              |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| R <sub>TH</sub> -based methods | (Ji, Song, Cao, Pickert, Hu, Mackersie & Pierce, 2014)<br>(Saha, Celaya, Wysocki & Goebel, 2009)                                                                                                                                                                                                                                             | Chip solder<br>DBC solder                      |

| Voltage at high current        | <ul> <li>(Celaya, Saxena, Wysocki, Saha &amp; Goebel, 2010)</li> <li>(Ji, Pickert, Cao &amp; Zahawi, 2013)</li> <li>(Smet, Forest, Rached &amp; Richardeau, 2012)</li> <li>(Beczkowski, Ghimre, De Vega, Munk-Nielsen, Rannestad &amp; Thogersen, 2013)</li> <li>(Ghimire, De Vega, Munk-Nielsen, Rannestad &amp; Thogersen 2013)</li> </ul> | Wire-bond<br>Reconstruction of<br>metalization |

Table 2. Damage-Sensitive Electrical Parameters (DSEP)

## 5.3. Model-based approach

In the model-based approach, a training data set from other devices is used to model the evolution of the DSEP with time. The model can either be empirical or physical and is established after accelerated aging experiments on other devices and/or simulations. The prognostic algorithm uses the model and the measurements on the DUT to estimate the health and the RUL. Prognostic methods used in the literature are mainly Extended Kalman Filter (EKF) and Particle Filter (PF) (Baraldi, Maio & Zio, 2014).

In (Celaya, Saxena, Saha & Goebel, 2011), (Patil, Das & Pecht, 2012), and (Saha, Celaya, Vashchenko, mahiuddin & Goebel, 2011), several aged discrete devices are used to fit an empirical model of the evolution of  $R_{DS-ON}$ ,  $V_{CE-ON}$ , and V<sub>TH</sub> respectively. The observations on the DUT are related to the empirical models with a particle filter to estimate the degradation state. In (Alghassi, Perinpanayagam & Samie, 2015), an alternative to EKF and PF is proposed. The V<sub>CE-ON</sub> value is decomposed into 9 discrete steps. A training dataset of 3 discrete IGBTs is used to provide a statistical distribution for the duration of each state. It is then used with Monte-Carlo simulations to investigate a statistical RUL prediction. The result is a light-weight simulationbased prognostic approach requiring only 0.3ms computation time for each measurement.

### 6. POTENTIAL OF PROGNOSTICS FOR POWER MODULES

The cost associated with the implementation of prognostic means in a power module has to be counterbalanced with quantifiable benefits. First, the prognostic information can be used in order to develop cost-optimized minimumintervention and just-in-time maintenance strategies. Second, active health management can be employed to redistribute the stress to extend the life time of a device based on prognostic information.

## 6.1. Asset Management

Two asset-management strategies are commonly used in the field of power electronics: replacement after failure, and replacement at fixed intervals (in mission critical applications). Prognostic is a key enabler to asset management that ensures a good compromise between the risk of failure and the return on investment.

The development of a business model is necessary to support asset management. Return on investment calculations were applied to various electronic products (Sandborn & Wilkinson, 2007), (Feldman, 2009) and (Haddad, Sandborn & Pecht, 2014) but no business case was published for power modules until now. The main difficulty of establishing a business model is to estimate all costs additions (non-recurring, recurring, infrastructure) and cost avoidances (failure cost, maintenance cost) that are used by the stochastic simulator.

Manufacturers of power modules are facing problems to provide users with a year-based warranty. This is because of the considerable impact of system integration, operating and environmental conditions. Manufacturers would more easily provide a warranty based on applied stressors, such as number of junction temperature cycles.

## 6.2. Active stress reduction or redistribution

Stress reduction limits the performances of the system in order to extend the life time. The most straightforward implementation consists in de-rating (load current, operating voltage) of the module. This approach increases the system costs, and other solutions are preferred (Table 3). Several methods are commonly combined to offer various degrees of lifetime control. These methods can be used as a protection for over-temperature T<sub>JMAX</sub>, and as a mean to decrease power cycling stress, reducing the  $\Delta T_{I}$  around T<sub>IMEAN</sub> value. Another type of active control consists in controlling the minimum case temperature for the power module. Hence, as the fluctuations of junction temperature are reduced (Davidson, Stone & Foster, 2014) the lifetime of the module should increase, but no study was yet performed to evaluate CTE mismatch decrease and lifetime gain. Lastly, while the redistribution of stress between distinct power modules is not covered by this paper, some methods have been demonstrated for actively controlling parallel power modules (Hofer, Karrer and Gerster, 1996). However, it should be noted that for the latter method, the aim is to equalize the current distribution across the parallel set of modules, rather than to directly control the temperature to increase the lifetime of the module.

| Parameter                  | Description                   | Downside                 | References                                                                |

|----------------------------|-------------------------------|--------------------------|---------------------------------------------------------------------------|

| Load current               | Decrease<br>conduction losses | Load current decrease    | (Blasko, Lukaszewski & Sladky, 1999)<br>(Murdock, Torres & Connors, 2006) |

|                            | conduction losses             |                          | (Lemmens, Driesen & Vanassche, 2012)                                      |

| Switching frequency        | Decrease switching            | Load ripple increase     | (Blasko et al. 1999)                                                      |

|                            | losses                        |                          | (Murdock et al. 2006)                                                     |

|                            |                               |                          | (Lemmens et al. 2012)                                                     |

|                            |                               |                          | (Weckert & Roth-Stielow, 2011)                                            |

|                            |                               |                          | (Wei, McGuire & Lukaszewski, 2011)                                        |

|                            |                               |                          | (Lo Calzo, Lidozzi, Solero, Crescimbini & Cardi, 2012)                    |

| DC-link voltage regulation | Decrease                      | Oversized actives and    | (Andresen & Liserre, 2014)                                                |

|                            | conduction losses             | passives, risk for       |                                                                           |

|                            |                               | random failures          |                                                                           |

| Modulation strategy        | Modify modulation             | EMI difficult to control | (Lo Calzo et al. 2012)                                                    |

|                            | type                          |                          | (Ma & Blaabjerg, 2014)                                                    |

|                            | (continuous/disconti          |                          |                                                                           |

|                            | nuous) or pattern             |                          |                                                                           |

| Active gate driving        | Increase the gate             | Potential gate oxide     | (Wu & Castellazzi 2010)                                                   |

|                            | voltage                       | degradation              |                                                                           |

| Heatsink                   | Increase cooling              | Oversized cooling        | (Law & Harley 2004)                                                       |

|                            | effort                        | system                   | (James, 2012)                                                             |

|                            |                               | Efficacy not proven      | (De Rijck & Huisman, 2013)                                                |

|                            |                               |                          | (Davidson et al. 2014)                                                    |

Table 3. Thermal and lifetime control techniques

## 7. CONCLUSION

As a result of increasing market penetration of power modules, the motivation to better understand their lifetime and health is paramount to continuing this trend. Hence, this paper presented a review of prognostic methods, starting with failure mechanisms and continuing with methods of counting stress or directly measuring the state of health.

#### REFERENCES

- Aal, A. (2014). A New Rainflow free Method to Transfer Irregular Load Mission Profile Data Into appropriate Lab Test Conditions for Design Optimization. *CIPS* 2014, (February), 25–27. Retrieved from http://ieeexplore.ieee.org/xpls/abs\_all.jsp?arnumber=67 76847

- Alghassi, A., Perinpanayagam, S., Samie, M., & Sreenuch, T. (2015). Computationally Efficient, Real-Time, and Embeddable Prognostic Techniques for Power Electronics. *IEEE Transactions on Power Electronics*, 30(5), 2623–2634. doi:10.1109/TPEL.2014.2360662

- Amro, R., Lutz, J., Rudzki, J., Sittig, R., & Thoben, M. (2006). Power Cycling at High Temperature Swings of Modules with Low Temperature Joining Technique. *ISPSD 2006*. doi:10.1109/ISPSD.2006.1666110

- Andresen, M., & Liserre, M. (2014). Impact of active thermal management on power electronics design. *Microelectronics Reliability*, 5–9. doi:10.1016/j.microrel.2014.07.069

- Avenas, Y., Dupont, L., & Khatir, Z. (2012). Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters—A Review.

*IEEE Transactions on Power Electronics*, 27(6), 3081–3092. doi:10.1109/TPEL.2011.2178433

- Bahun, I., Sunde, V., & Jakopovic, Z. (2013). Estimation of insulated-gate bipolar transistor operating temperature: Simulation and experiment. *Journal of Power Electronics*, 13(4), 729–736. doi:10.6113/JPE.2013.13.4.729

- Baker, N., Liserre, M., Dupont, L., & Avenas, Y. (2014). Improved Reliability of Power Modules: A Review of Online Junction Temperature Measurement Methods. *IEEE Industrial Electronics Magazine*, 8(September), 17–27. doi:10.1109/MIE.2014.2312427

- Baker, N., Munk-Nielsen, S., Liserre, M., & Iannuzzo, F. (2014). Online junction temperature measurement via internal gate resistance during turn-on. *ECPE 2014* (pp. 1–10). IEEE. doi:10.1109/EPE.2014.6911024

- Baraldi, P., Maio, F. Di, & Zio, E. (2014). Particle filters for prognostics. In *PHME 2014, Nantes, France*.

- Barlini, D., & Ciappa, M. (2006). New technique for the measurement of the static and of the transient junction temperature in IGBT devices under operating conditions. *Microelectronics Reliability*. doi:doi:10.1016/j.microrel.2006.07.058

- Barlini, D., & Ciappa, M. (2007). Measurement of the transient junction temperature in MOSFET devices under operating conditions. *Microelectronics Reliability*. doi:doi:10.1016/j.microrel.2007.07.008

- Barlow, T., Latham, S., McCrae, I., & Boulter, P. (2009). A reference book of driving cycles for use in the measurement of road vehicle emissions.

- Bayerer, R., Herrmann, T., Licht, T., Lutz, J., & Feller, M. (2008). Model for Power Cycling lifetime of IGBT

Modules - various factors influencing lifetime. In CIPS 2008.

- Beczkowski, S., Ghimre, P., de Vega, A. R., Munk-Nielsen, S., Rannestad, B., & Thogersen, P. (2013). Online Vce measurement method for wear-out monitoring of high power IGBT modules Keywords Off-line Vce measurement method. *EPE 2013*.

- Biela, J., Waffler, S., & Kolar, J. W. (2009). Mission profile optimized modularization of hybrid vehicle DC/DC converter systems. *PEMC* 2009, 1390–1396. doi:10.1109/IPEMC.2009.5157601

- Blasko, V., Lukaszewski, R., & Sladky, R. (1999). On line thermal model and thermal management strategy of a three phase voltage source inverter. *IAS 1999*, 2. doi:10.1109/IAS.1999.801687

- Bryant, A., Yang, S., Mawby, P., Xiang, D., Ran, L., Tavner, P., & Palmer, P. R. (2011). Investigation Into IGBT dV/dt During Turn-Off and Its Temperature Dependence. *IEEE Transaction on Power Electronics*, 26, 3019–3031. doi:10.1109/TPEL.2011.2125803

- Celaya, J. R., Saxena, A., Saha, S., Vashchenko, V., & Goebel, K. (2011). Prognostics of power MOSFET. In *ISPSD* 2011 (pp. 160–163). IEEE. doi:10.1109/ISPSD.2011.5890815

- Celaya, J. R., Saxena, A., Wysocki, P., Saha, S., & Goebel, K. (2010). Towards Prognostics of Power MOSFETs: Accelerated Aging and Precursors of Failure. In *PHMC* 2010 (pp. 0–10).

- Celaya, J., Saxena, A., Saha, S., & Goebel, kai F. (2011). Prognostics of Power MOSFETs under Thermal Stress Accelerated Aging using Data-Driven and Model-Based Methodologies. In *PHMC 2011* (pp. 1–10).

- Chen, H., Pickert, V., Atkinson, D., & Pritchard, L. (2006). On-line monitoring of the MOSFET device junction temperature by computation of the threshold voltage. In *PEMD 2006*.

- Davidson, J. N., Stone, D. a, & Foster, M. P. (2014). Realtime temperature monitoring and control for power electronic systems under variable active cooling by characterisation of device thermal transfer impedance. In *PEMD 2014* (pp. 1–6). doi:10.1049/cp.2014.0496

- De Rijck, A. C., & Huisman, H. (2013). Power semiconductor device adaptive assembly. NL. Patent US 8,547,687 B2.

- Dupont, L., Avenas, Y., & Jeannin, P.-O. (2013). Comparison of Junction Temperature Evaluations in a Power IGBT Module Using an IR Camera and Three Thermosensitive Electrical Parameters. *IEEE Transactions on Industry Applications*, 49(4), 1599– 1608. doi:10.1109/TIA.2013.2255852

- Feldman, K. (2009). A methodology for determining the return on investment associated with prognostics and health management. *IEEE Transactions on Reliability*, 58(2), 305–316.

- Ghimire, P., Ruiz de Vega, A., Munk-Nielsen, S., Rannestad, B., & Thogersen, P. B. (2013). A real time

Vce measurement issues for high power IGBT module in converter operation. *In 2013 1st International Future Energy Electronics Conference (IFEEC)* (pp. 761–766). IEEE. doi:10.1109/IFEEC.2013.6687604

- Goehre, J., Schneider-Ramelow, M., Geisler, U., & Lang, K.-D. (2010). Interface degradation of Al heavy wire bonds on power semiconductors during active power cycling measured by the shear test. *IPES 2010*, 1–6.

- Haddad, G., Sandborn, P. a., & Pecht, M. G. (2014). Using maintenance options to maximize the benefits of prognostics for wind farms. *Wind Energy*, 17(5), 775– 791. doi:10.1002/we.1610

- Halford, G., & Manson, S. (1967). A method of estimating high temperature low cycle fatigue behavior of materials. *Symposium on Thermal and High Streain Fatigue*, 1967.

- Held, M., Jacob, P., Nicoletti, G., Scacco, P., & Poech, M.-H. (1997). Fast power cycling test of IGBT modules in traction application. *PEDS* 1997, 1. doi:10.1109/PEDS.1997.618742

- Hensler, A., Lutz, J., Thoben, M., & Guth, K. (2010). First power cycling results of improved packaging technologies for hybrid electrical vehicle applications. *IPES 2010*, 1–5.

- Herrmann, T., Feller, M., Lutz, J., Bayerer, R., & Licht, T. (2007). Power cycling induced failure mechanisms in solder layers. In *EPE* 2007. doi:10.1109/EPE.2007.4417702

- Hirschmann, D., Tissen, D., Schröder, S., & De Doncker, R. W. (2007). Reliability prediction for inverters in hybrid electrical vehicles. *IEEE Transactions on Power Electronics*, 22(6), 2511–2517. doi:10.1109/TPEL.2007.909236

- Huang, H., & Mawby, P. a. (2013). A lifetime estimation technique for voltage source inverters. *IEEE Transactions on Power Electronics*, 28(8), 4113–4119. doi:10.1109/TPEL.2012.2229472

- Hofer, P., Karrer, N., & Gerster, C. (1996). Paralleling intelligent IGBT power modules with active gatecontrolled current balancing. *PESC 1996*, 2, 1312– 1316. doi:10.1109/PESC.1996.548751

- James, P. (2012). *Health Monitoring of IGBTs in Automotive Power Converter Systems*. PHD Thesis. University of Manchester.

- Ji, B. (2011). In-situ Health Monitoring of IGBT Power Modules in EV Applications. PhD Thesis. Newcastle University.

- Ji, B., Pickert, V., Cao, W., & Zahawi, B. (2013). In situ diagnostics and prognostics of wire bonding faults in IGBT modules for electric vehicle drives. *IEEE Transactions on Power Electronics*, 28(12), 5568– 5577. doi:10.1109/TPEL.2013.2251358

- Ji, B., Song, X., Cao, W., Pickert, V., Hu, Y., Mackersie, J.,

& Pierce, G. (2014). In-Situ Diagnostics and Prognostics of Solder Fatigue in IGBT Modules for

Electric Vehicle Drives. *IEEE Transactions on Power Electronics*, *PP*(3), 1. doi:10.1109/TPEL.2014.2318991

- Kim, Y.-S. K. Y.-S., & Sul, S.-K. S. S.-K. (1998). On-line estimation of IGBT junction temperature using on-state voltage drop. *IAS* 1998, 2, 853–859. doi:10.1109/IAS.1998.730245

- Koenig, A., Plum, T., Fidler, P., & De Doncker, R. W. (2007). On-line junction temperature measurement of coolmos devices. In *PEDS* 2007 (pp. 90–95). doi:10.1109/PEDS.2007.4487683

- Kovačević, I. F., Drofenik, U., & Kolar, J. W. (2010). New physical model for lifetime estimation of power modules. *IPEC* 2010, 2106–2114. doi:10.1109/IPEC.2010.5543755

- Kovaltchouk, T., Aubry, J., Multon, B., & Ben Ahmed, H. (2013). Influence of IGBT current rating on the thermal cycling lifetime of a power electronic active rectifier in a direct wave energy converter. *EPE 2013*. doi:10.1109/EPE.2013.6631903

- Kuhn, H., & Mertens, A. (2009). On-line junction temperature measurement of IGBTs based on temperature sensitive electrical parameters. *EPE 2009*. Law, J. M., & Harley, N. H. (2004). Active thermal management of semiconductor devices. USA.

- Lemmens, J., Driesen, J., & Vanassche, P. (2012). Thermal management in traction applications as a constraint optimal control problem. *VPPC 2012*, (including DC), 36–41. doi:10.1109/VPPC.2012.6422652

- Lo Calzo, G., Lidozzi, A., Solero, L., Crescimbini, F., & Cardi, V. (2012). Thermal regulation as control reference in electric drives. In *EPE-PEMC 2012* (pp. 1–7). doi:10.1109/EPEPEMC.2012.6397302

- Lu, H., Bailey, C., & Yin, C. (2009). Design for reliability of power electronics modules. *Microelectronics Reliability*, 49(9-11), 1250–1255. doi:10.1016/j.microrel.2009.07.055

- Lutz, J., Paul, S., & Zill, J. (2011). Junction temperature determining method for e.g. insulated-gate bipolar transistor in three-phase power converter arrangement, involves supplying current to be fed so that total current flowing in transistor corresponds to test current. Germany. Patent DE102010000875B4.

- Lutz, J., Schlangenotto, H., Scheuermann, U., & De Doncker, R. (2011). Semiconductor power devices: Physics, characteristics, reliability. Berlin, Heidelberg: Springer Berlin Heidelberg. doi:10.1007/978-3-642-11125-9

- Ma, K., & Blaabjerg, F. (2014). Modulation methods for neutral-point-clamped wind power converter achieving loss and thermal redistribution under low-voltage ridethrough. *IEEE Transactions on Industrial Electronics*, 61, 835–845. doi:10.1109/TIE.2013.2254099

- Ma, K., Liserre, M., Blaabjerg, F., & Kerekes, T. (2014). Thermal Loading and Lifetime Estimation for Power Device Considering Mission Profiles in Wind Power

Converter. *IEEE Transactions on Power Electronics*, 8993(c), 1–1. doi:10.1109/TPEL.2014.2312335

- Madjour, K. (2014). Silicon Carbide market update : From discrete devices to modules.... In *PCIM* 2014. Nuremberg.

- Mainka, K., Thoben, M., & Schilling, O. (2011). Lifetime calculation for power modules, application and theory of models and counting methods. *EPE 2011*, 1–8.

- Miner, M. (1945). Cumulative damage in fatigue. *Journal of Applied Mechanics*, 67, A159–A164.

- Morozumi, a., Yamada, K., Miyasaka, T., Sumi, S., & Seki, Y. (2003). Reliability of power cycling for igbt power semiconductor modules. *IEEE Transactions on Industry Applications*, 39(3), 665–671. doi:10.1109/TIA.2003.810661

- Motto, E. R., & Donlon, J. F. (2012). IGBT module with user accessible on-chip current and temperature sensors. *APEC* 2012, 176–181. doi:10.1109/APEC.2012.6165816

- Murdock, D. a., Torres, J. E. R., Connors, J. J., & Lorenz, R. D. (2006). Active thermal control of power electronic modules. *IEEE Transactions on Industry Applications*, 42(2), 552–558. doi:10.1109/TIA.2005.863905

- Musallam, M., Johnson, C. M., Yin, C., Bailey, C., & Mermet-Guyennet, M. (2010). Real-time life consumption power modules prognosis using on-line rainflow algorithm in metro applications. In *ECCE* 2011 (pp. 970–977). IEEE. doi:10.1109/ECCE.2010.5617883

- Musallam, M., Yin, C., Bailey, C., & Johnson, M. (2015). Mission Profile-Based Reliability Design and Real-Time Life Consumption Estimation in Power Electronics. *IEEE Transactions on Power Electronics*, 30(5), 2601–2613. doi:10.1109/TPEL.2014.2358555

- Niu, H., & Lorenz, R. D. (2013). Sensing power MOSFET junction temperature using circuit output current ringing decay. *In ECCE 2013* (pp. 4270–4277). doi:10.1109/ECCE.2013.6647271

- Niu, H., & Lorenz, R. D. (2015). Sensing IGBT junction temperature using gate drive output transient properties. *In 2015 IEEE Applied Power Electronics Conference and Exposition (APEC)* (pp. 2492–2499). IEEE. doi:10.1109/APEC.2015.7104700

- Onuki, J., Koizumi, M., & Suwa, M. (2000). Reliability of thick Al wire bonds in IGBT modules for traction motor drives. *IEEE Transactions on Advanced Packaging*, 23(1), 108–112. doi:10.1109/6040.826768

- Patil, N., Das, D., & Pecht, M. (2012). A prognostic approach for non-punch through and field stop IGBTs. *Microelectronics Reliability*, 52(3), 482–488. doi:10.1016/j.microrel.2011.10.017

- Perpiñà, X., Serviere, J. F., Saiz, J., Barlini, D., Mermet-Guyennet, M., & Millán, J. (2006). Temperature measurement on series resistance and devices in power packs based on on-state voltage drop monitoring at high

current. *Microelectronics Reliability*, 46(9-11), 1834–1839. doi:10.1016/j.microrel.2006.07.078

- Rashed, A., Forest, F., Huselstein, J. J., Martire, T., & Enrici, P. (2013). On-line [TJ, Vce] monitoring of IGBTs stressed by fast power cycling tests. In *EPE* 2013 (pp. 1–9). doi:10.1109/EPE.2013.6631965

- Saha, B., Celaya, J. R., Wysocki, P. F., & Goebel, K. F. (2009). Towards prognostics for electronics components. *IEEE Aerospace Conference*, 1–7. doi:10.1109/AERO.2009.4839676

- Saha, S., Celaya, J. R., Vashchenko, V., Mahiuddin, S., & Goebel, K. F. (2011). Accelerated aging with electrical overstress and prognostics for power MOSFETs. *ENERGYTECH* 2011, 1–6. doi:10.1109/EnergyTech.2011.5948532

- Sandborn, P. a., & Wilkinson, C. (2007). A maintenance planning and business case development model for the application of prognostics and health management (PHM) to electronic systems. *Microelectronics Reliability*, 47(12), 1889–1901. doi:10.1016/j.microrel.2007.02.016

- Scheuermann, U., & Schmidt, R. (2011). Impact of solder fatigue on module lifetime in power cycling tests. *EPE* 2011.

- Schuler, S. (2011). Semiconductor assembly and method for determining the barrier layer temperature of a semiconductor component. Germany. Patent EP2302673 A2.

- Singleton, R. K., Strangas, E. G., & Aviyente, S. (2015). Extended Kalman Filtering for Remaining-Useful-Life Estimation of Bearings. *IEEE Transactions on Industrial Electronics*, 62(3), 1781–1790. doi:10.1109/TIE.2014.2336616

- Smet, V., Forest, F., Huselstein, J. J., Rashed, A., & Richardeau, F. (2013). Evaluation of Vce monitoring as a real-time method to estimate aging of bond wire-IGBT modules stressed by power cycling. *IEEE Transactions on Industrial Electronics*, 60(7), 2760– 2770. doi:10.1109/TIE.2012.2196894

- Sundaramoorthy, V., Bianda, E., Bloch, R., Nistor, I., Knapp, G., & Heinemann, A. (2013). Online estimation of IGBT junction temperature (Tj) using gate-emitter voltage (Vge) at turn-off. *EPE 2013* (pp. 1–10). IEEE. doi:10.1109/EPE.2013.6634444

- Sundaramoorthy, V. K., Bianda, E., Bloch, R., & Zurfluh, F. (2014). Simultaneous online estimation of junction temperature and current of IGBTs using emitterauxiliary emitter parasitic inductance. *In PCIM Europe* (pp. 1–8).

- Thoben, M., Mainka, K., Bayerer, R., Graf, I., & M.Munzer. (2008). From Vehicle Drive Cycle to Reliability Testing of Power Modules. *Automotive Power*, (6), 6–9.

- Weckert, M., & Roth-Stielow, J. (2011). Chances and limits of a thermal control for a three-phase voltage source inverter in traction applications using permanent

magnet synchronous or induction machines. *EPE 2011*, 1–10.

- Wei, L., McGuire, J., & Lukaszewski, R. a. (2011). Analysis of PWM frequency control to improve the lifetime of PWM inverter. *IEEE Transactions on Industry Applications*, 47(2), 922–929. doi:10.1109/TIA.2010.2103391

- Wintrich, A., Nicolai, U., Tursky, W., & Reimann, T. (2011). *Application Manual Power Semiconductors*. (Semikron, Ed.).

- Wu, L., & Castellazzi, A. (2010). Temperature adaptive driving of power semiconductor devices. *ISIE 2010*, 1110–1114. doi:10.1109/ISIE.2010.5636541

- Wu, W. W., Held, M., Jacob, P., Scacco, P., & Birolini,

A. (1995). Investigation on the long term reliability of power IGBT modules. *ISPSD* 1995. doi:10.1109/ISPSD.1995.515079

- Xiang, D., Ran, L., Tavner, P., Yang, S., Bryant, A., & Mawby, P. (2012). Condition monitoring power module solder fatigue using inverter harmonic identification. *IEEE Transactions on Power Electronics*, 27(1), 235– 247. doi:10.1109/TPEL.2011.2160988

- Xu, Z., Jiang, D., Li, M., Ning, P., Wang, F. F., & Liang, Z. (2013). Development of Si IGBT phase-leg modules for operation at 200 °C in hybrid electric vehicle applications. *IEEE Transactions on Power Electronics*, 28(12), 5557–5567. doi:10.1109/TPEL.2013.2242096

- Yang, S., Bryant, A., Mawby, P., Xiang, D., Ran, L., & Tavner, P. (2011). An Industry-Based Survey of Reliability in Power Electronic Converters. *IEEE Transaction On Industry Applications*, 47(3), 1441– 1451. doi:10.1109/TIA.2011.2124436

- Yang, S., Xiang, D., Bryant, A., Mawby, P., Ran, L., & Tavner, P. (2010). Condition Monitoring for Device Reliability in Power Electronic Converters: A Review. *Power Electronics, IEEE Transactions on*, 25(11), 2734–2752. doi:10.1109/TPEL.2010.2049377

- Yang, Y., Wang, H., & Blaabjerg, F. (2015). Reliability Assessment of Transformerless PV Inverters Considering Mission Profiles. *International Journal of Photoenergy*.